LED ControllerブロックのサンプルHDLコードを論理合成用の作業ディレクトリICCにコピーする。

vlsi> cd ~/d vlsi> cp -r sample/verilog6 ICC vlsi> cd ICC

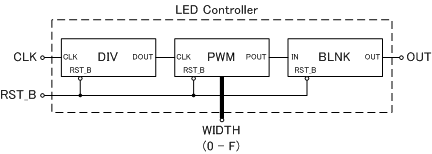

モジュール構成

Verilog HDLファイル構成

| ファイル名 | 機能 |

|---|---|

| div.v | (214-1)分周器(クロック周波数を下げる) |

| pwm.v | 4bit PWM(輝度調整) |

| blnk.v | 512PWM周期 Duty ratio = 0.5(LED点滅) |

| led.v | LED Controller全体 |

| tb_led.v | led.vのテストベンチ(シミュレーション用) |

シミュレータに入力するHDLファイルを指定するための、入力ファイルリストを記載したファイルを作成する。ここでは、led.fというファイル名で下記の内容を記載する。

led.fの内容

tb_led.v (※) led.v div.v pwm.v blnk.v |

※ テストベンチは、最初に記載するとよい。この場合、`timescale をテストベンチファイルに記述しておけば、回路を記述したHDLファイルでは、`timescaleを省略してもよい。

コマンドラインで、Verilog-XLを起動する。setlicは、各ツールの環境設定を行う。shellに対して、最初の1回だけ実行すればよい。

vlsi> setlic Cadence INCISIVEに相当する番号を入力 vlsi> verilog +gui -s -f led.f &[参考] Verilog-XLのオプション

| +gui | GUIモードで起動 |

| -s | シミュレーションの前に一旦停止(モニタ信号などを指定できる) |

| -f | 入力ファイルリストを記入したファイルを指定 |

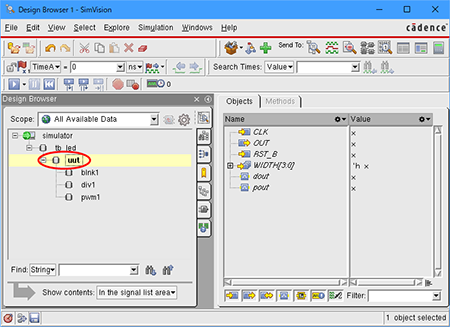

SimVisionでシミュレーション結果を確認する。左欄の+マークをクリックすると階層が展開される。この例では、テストベンチtb_ledの下にモジュールledのインスタンス uutが存在する。uutをクリックすると、uutの入出力信号名のリストが表示される。

この状態で、ツールバーのブロック図アイコンをクリックすると、ブロック図が表示される。ブロックをダブルクリックすると下位の階層のブロック図が表示される。

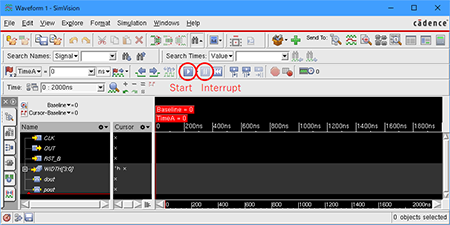

波形アイコンをクリックすると、Waveformビュワーが表示される。

Waveformビュワーの開始ボタンをクリック(上図参照)すると、シミュレーションが実行され、波形が表示される。=ボタンをクリックすると、シミュレーションされた波形全体が表示される。POUTのパルス幅が、徐々に増えていくのを確認する。確認できたら、開始ボタンの右側にある一時停止ボタンで止めてよい。

メニュー:File > Exit SimVisionを選んで終了する。