- ストリームファイルの読み込み

自動配置配線で作成したLED.str(または、LED.gds)をレイアウトエディタに読み込む。

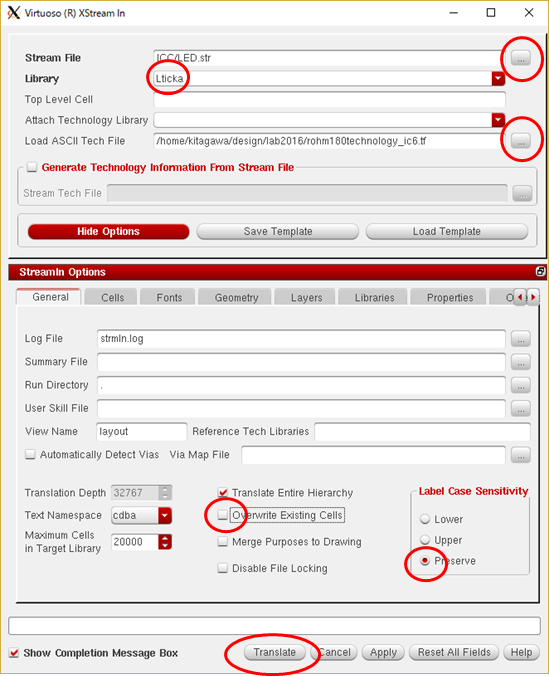

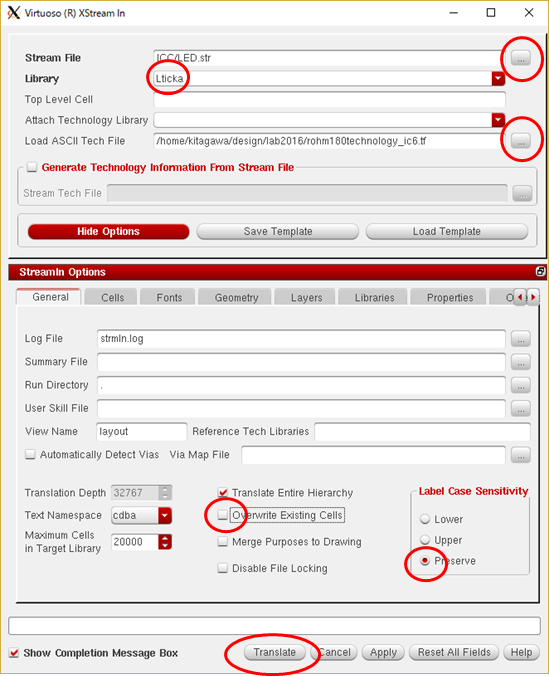

- CIWのメニューより、File > Import > Stream... を選択。

- Show Optionsボタンをクリックし、下記の設定を行う。

| Stream File | ICC/LED.str(自動配置配線ツールで作成) |

| Destination Library | Lticka(読み込み先のライブラリ) |

| Load ASCII Tech File | rohm180technology_ic6.tf(Cadence用テクノロジファイル) |

| Overwrite Existing Cells | チェックを外す |

| Label Case Sensitivity | Preserve |

- Translateボタンをクリック。

- PopUp Messageが表示されるので、エラーがないことを確認し、OKボタンをクリック。エラーがある場合は、Display Logをクリック。Warningが出ることがあるが、無視してよい。

- Layout Viewの作成

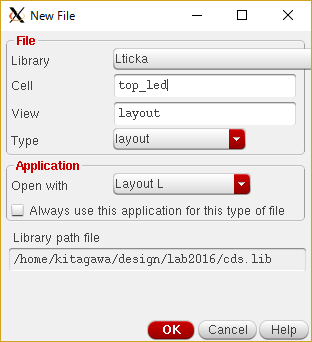

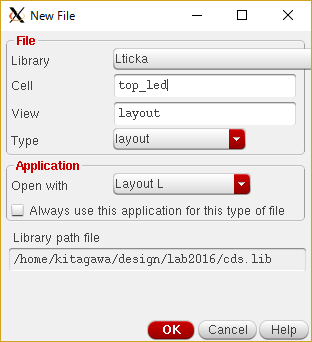

- Library Managerで、File > New > Cell View... を選択し、下図のように設定して、top_ledセルのlayout viewを作成。

- Layout XLは、回路図と照合しながらレイアウトを行う機能が内蔵されているが、今回は、トップの回路図を用意していないので、Layout L を使用する。

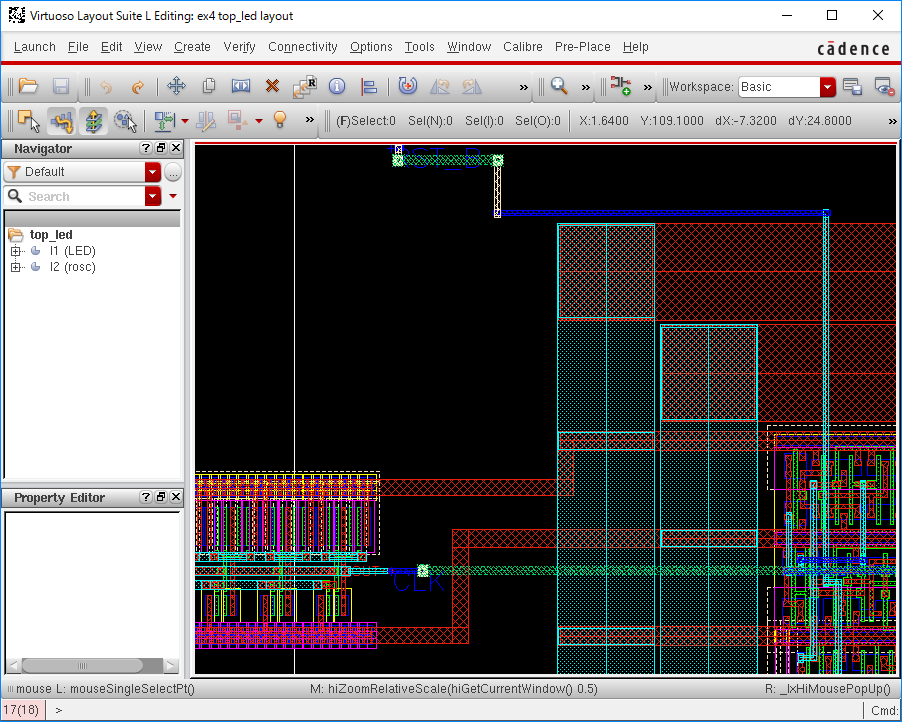

- Library Managerにtop_ledが追加され、レイアウトエディタが起動する。

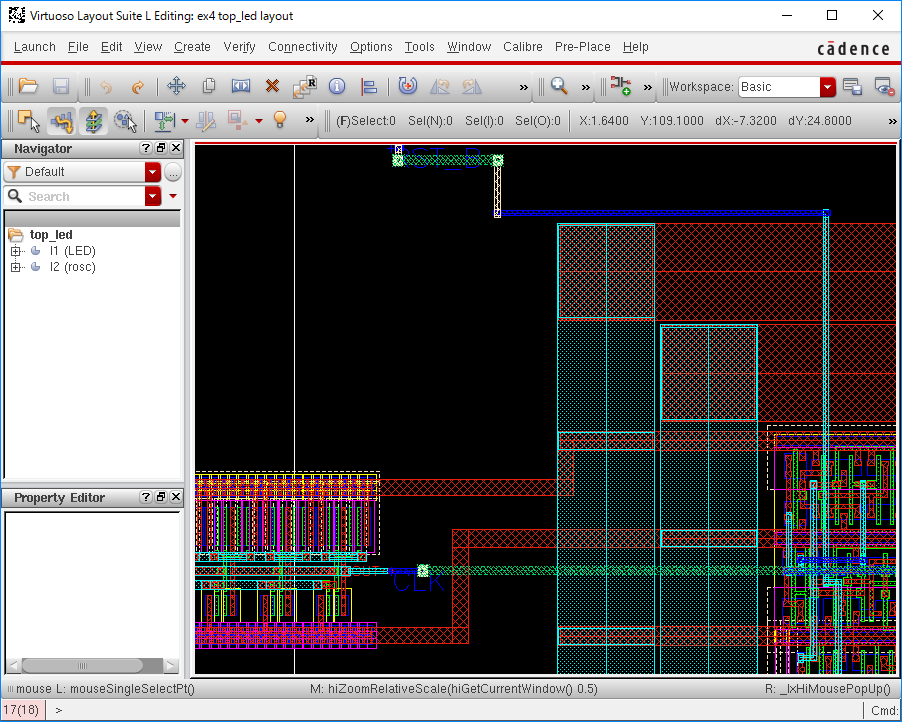

- 回路のつなぎ込み

- レイアウトエディタに、インスタンスとして、LEDとroscを呼び出して配置(iキー)。Instance配置コマンドを終了するには、ESCキーを押す。

- 電源VDD!, VSS!, OSC_CLK(rosc側)-CLK(LED側)を接続。

- LEDのCLK配線は、METAL5で引き出されている。一方、roscのOSC_CLKは、METAL2が使用されている。このため、METAL5-VIA4-METAL4-VIA3-METAL3-VIA2-METAL2のように、配線層間をVIAで繋ぐ必要がある。

- LED側のVDD!とVSS!は、ラベルが付けられていないが、解説書の手順通りに操作した場合、外側の電源リングがVDD!, 内側の電源リングがVSS!となる。

- スタンダードセル内の配線を確認して、VDD!とVSS!を判別することもできる。NWELLに接続がある方が、VDD!となる。

- top_ledを保存。

- コア回路全体のDRCを行う。

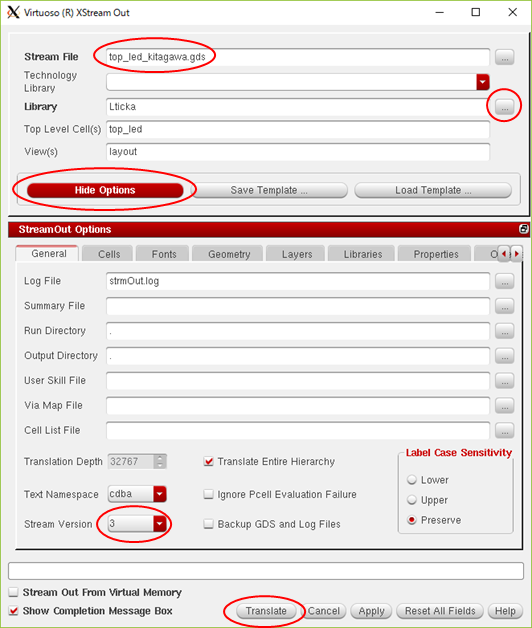

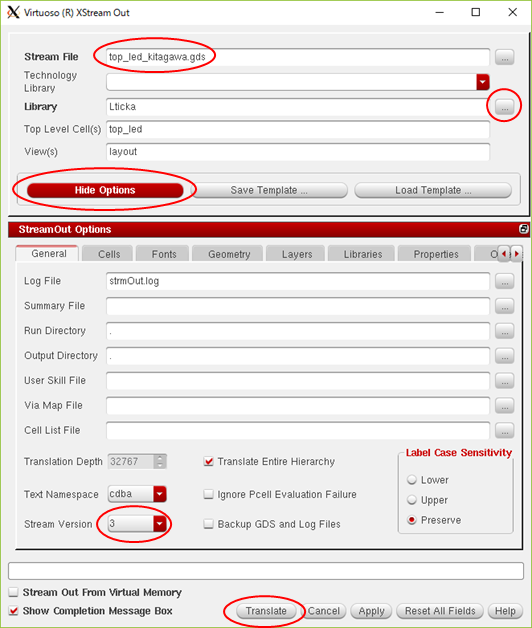

メーカに提出するためのGDS-IIフォーマットのデータを作成する。GDS-IIファイルは、ストリームファイルとも呼ばれる。通常は次項のフレームを設計してからチップ全体のストリームデータを出力するが、複数の設計を1チップに相乗りさせる場合は、コアの段階でストリームデータを出力し、チップ全体のとりまとめ担当者に渡すとよい。

- CIWのメニューより、File > Export > Stream... を選択。

- Virtuoso XStream Out フォームでStream File欄に出力するファイル名を入力。

- 拡張子は、gdsとする。

- 他の人のファイルと重ならないように、ファイル名に自分の名前などを含めること。

- Library欄右端の...ボタンをクリックし、出力するレイアウトデータを選択。

- 例: Library = Lticka, Cell = LED, View = layout

- Show Optionsボタンをクリック。

- Stream Version = 3 に変更(その他のオプションはデフォルト)。

- Translateボタンをクリック。

以上で、作業ディレクトリ内に、指定したファイル名で、GDS-IIフォーマットのファイルが出力されるので、ストリームデータ保存用ディレクトリに移動しておく。

vlsi> cd ~/d

vlsi> mkdir gds

vlsi> mv "ストリームデータファイル名" ./gds/

以下の設計工程は、チップ全体のプロジェクト管理者が実施する。トップ階層のレイアウトを行うためには、フレーム(チップの外形)、IOバッファ(入出力回路)、パッド(※)が必要になる。VDECでは、フレームにパッドが配置されたストリームファイルが提供されている。

※ パッドは、ワイヤーボンディングを行うための、表面にむき出しの電極であり、パッケージングする場合には、決められた位置に配置しなければならない。

トップ階層のレイアウトには、ある程度の経験が必要なため、以下に、概略手順のみを示す。

- パッド付きフレームを原点に置く。

- IOバッファを配置する。

- コア回路を適当な向きに配置する。

- コア回路の電源、IOピンとバッファまたはパッドをつなぎ込む。

- 全体のDRCを行う。

- デンシティルールチェックを行う。

- デンシティルールは、配線密度のチップ内均一性に対する制約条件であり、チップ全体に対してチェックを行う。これにパスしないと製造できない。

- トップ階層のストリームファイル出力。

- ストリームデータ(GDS-II)の提出。

- データの提出前に、大型プロッタでチップ全体のレイアウトを打ち出し、IOバッファと電源の配線を目視で確認することが推奨される。一人ではエラーに気づかないことが多いので、できるだけ多くのメンバーで確認した方がよい。

[Table of Contents] [Next]

お問い合わせはこちらまで: kitagawa@is.t.kanazawa-u.ac.jp

Copyright (C) 2016- Akio Kitagawa, Kanazawa Univ.