#### 3.3 Synchronization

# Removing a hazard and a timing control

# 3.3.1 Hazard in combinational logic

#### Example of single output

The 2-input logic generates the hazard (incorrect Truth table result) during the delay time of the signal path. a b С T=0T=0 0  $\mathbf{0}$ 0 0 0 1  $\cap$ 1 0 0 а а AND INV 0 b С b Hazard T=0 0 0 () С ()0 1 1 Delay of INV When the propagation delay = 0Delay of AND Delay of INV

3

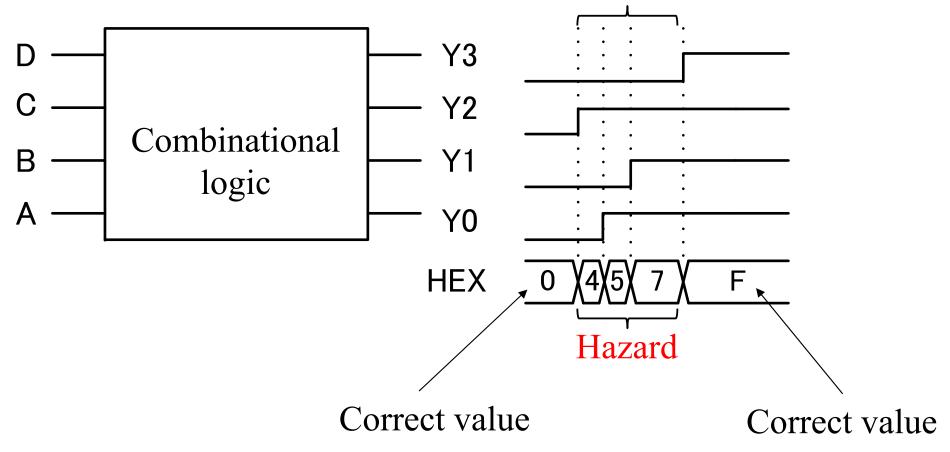

### Example of multiple output

The time-of-arrival of each output is different from each other.

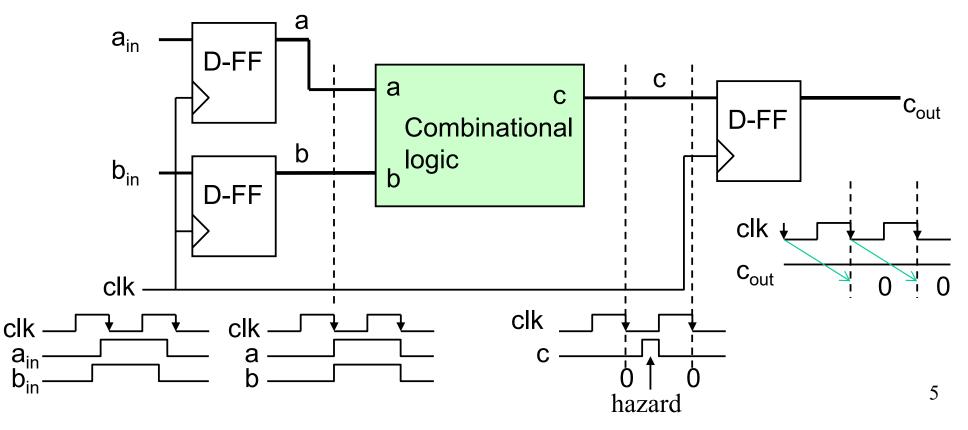

# Sequence control of combinational logic

- The hazard is removed by using a synchronizing clock.

- The logic synthesizers basically generates the synchronous circuits.

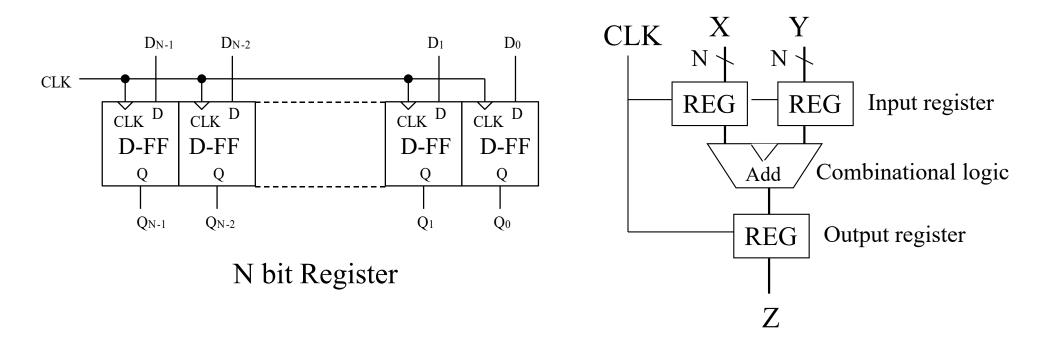

#### Circuit of register

I/O register Pipeline register Instruction register Address register

These registers synchronize any signals of ALU, IO and BUS.

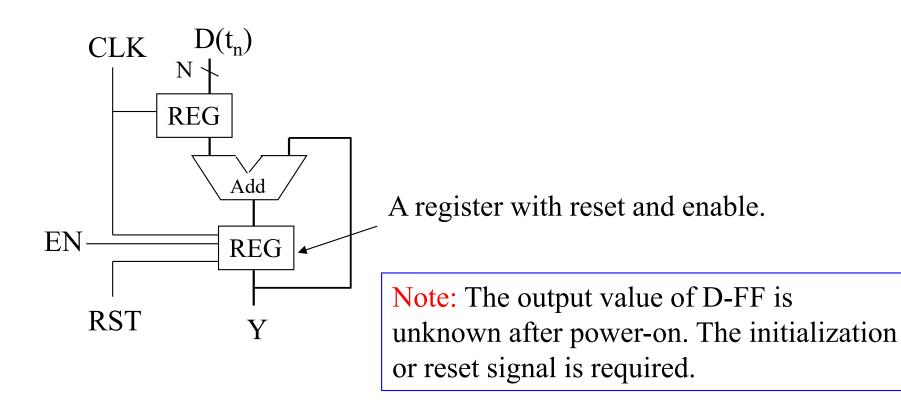

#### Accumulator

- 1. The registers are reset before accumulation.

- 2. This circuit performs an accumulation during EN = 1.

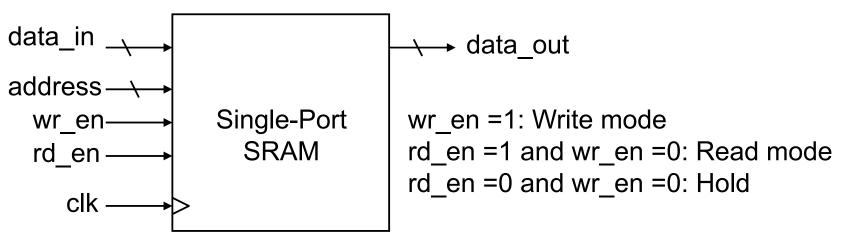

# Register and memory

- 2 types of embedded memoirs

- Register file

- consists of an array of registers and an address decoder . ← Synthesizable from HDL code.

- can be also implemented by using a high-speed multiport SRAM.

- SRAM (Static Random Access Memory)

- An SRAM is usually provided in the form of IP core.

- You can design a SRAM core, however, the knowledge of the transistor-level design is required.

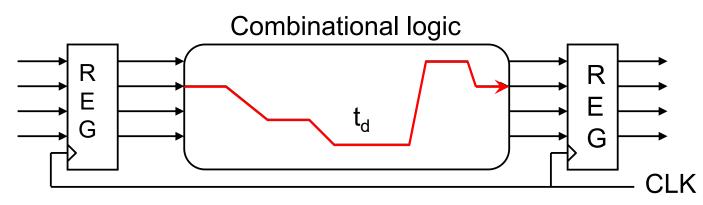

### 3.3.2 Maximum clock frequency

#### Maximum delay constraint

F(x)X2 X1 Combinational REG REG D2 **D**1 logic CLK CLK A signal propagation path which has a maximum delay time is called a D1 0 21 3 critical path of combinational logic. X1 0 2  $F(1)_{i}$ F(2) F(0) X2 Constraint:  $t_d < T_{clk}$ td td The result is output F(0) F(2) Х F(1) D2 ► after one clock cycle. T<sub>clk</sub> 10 T<sub>clk</sub>

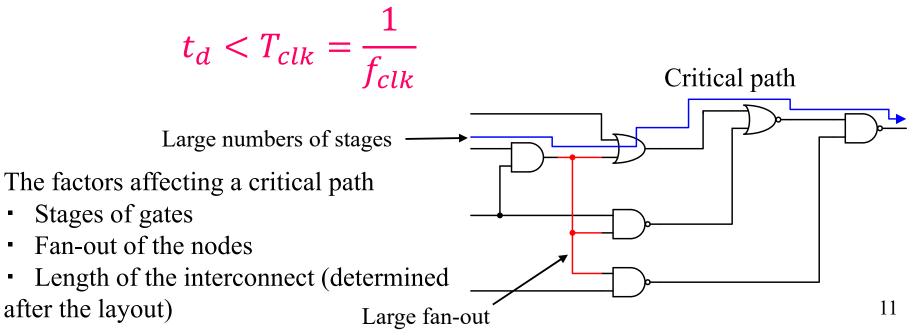

### The factors affecting a critical path

The delay time  $t_d$  of the signal propagation through the critical path is longest. The delay time of the critical path must be smaller than the period of the clock signal.

#### Improvements of a critical path

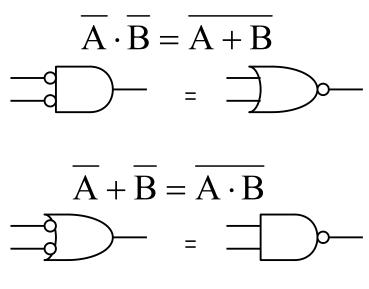

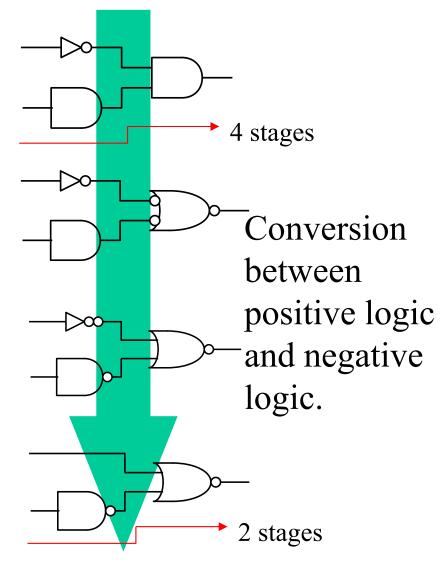

De Morgan's theorem

Note: Do not carry out the optimization of logic stages manually. This procedure should be left to CAD software.

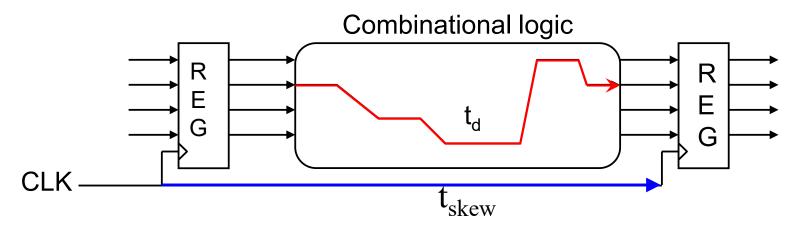

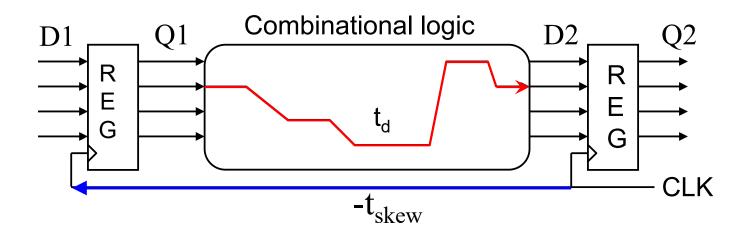

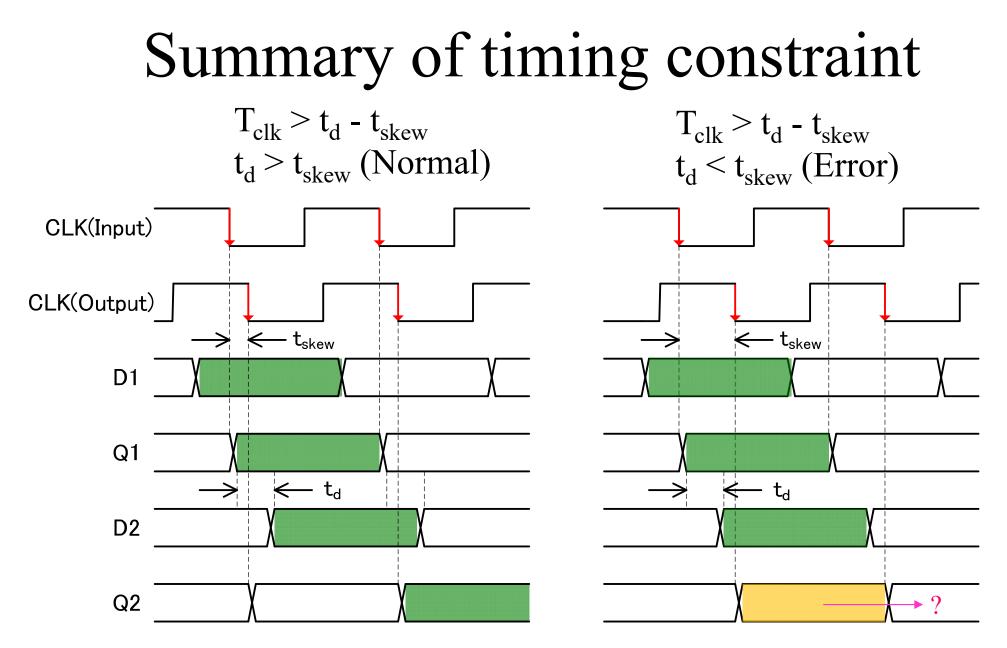

#### Clock skew

A phenomenon in synchronous digital circuit in which the same sourced clock signal arrives at different components at different times.

If  $t_d < t_{skew}$ , the result of the combinational logic is output from the output resistor in the same clock cycle as input cycle. (The result should be output one cycle later.)

## Racing

A clock skew causes a racing between the signal in the combinational logic and the clock signal.

$t_d < t_{skew}$  (Previous slide) : An error occurs by racing.  $t_d > 0 > -t_{skew}$  (See the illustration): The circuit operates normally.

# STA (Static Timing Analysis)

- STA and logic simulation

- The delay time can be calculated by STA and logic simulation.

- In STA, the delay time is calculated from the number of the stages and the number of fanout through the critical path.

- STA has an advantage in comparison with the timing simulation, because the it does not require the test vector and does not take a lot of time.

- STA satisfy the timing constraints for the logic synthesis.

- Propagation delay of logic gates and wires

- A prorogation delay is a total of a gate delay and a wiring delay.

- A gate delay is estimated by a delay information of each gates.

- A wiring delay is estimated by a delay model based on a statistical data which associates a delay time with a wiring length.

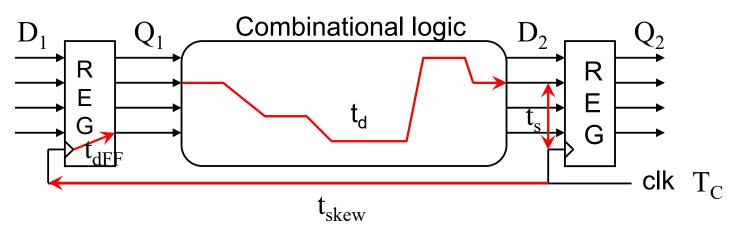

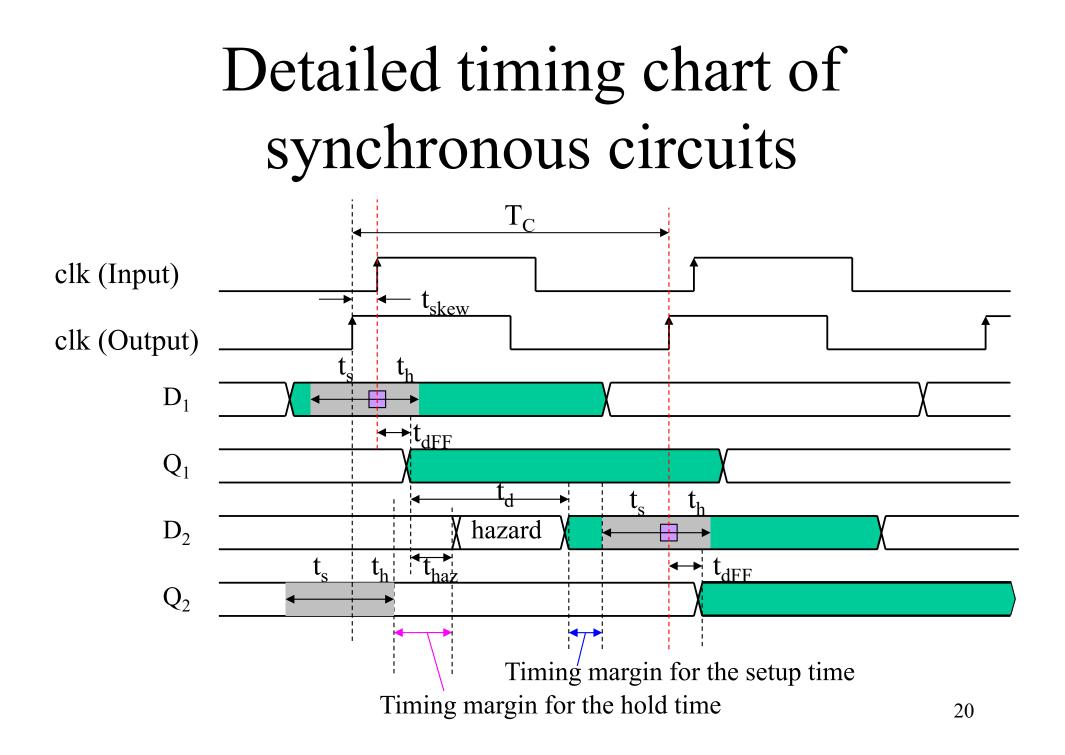

# 3.3.3 Detail of the timing constraint

# Timing constraints of synchronous circuits 1

| t <sub>dFF</sub> : | Delay time | of the register |

|--------------------|------------|-----------------|

| агг                |            |                 |

Delay time of the critical path t<sub>d</sub>:

Clock skew (Note the transmitting direction of the clock.) t<sub>skew</sub>: t<sub>s</sub>: Setup time of the register

$T_{C} > t_{dFF} + t_{d} + t_{skew} + t_{s}$  (Setup time constraint)

Large combinational logic: t<sub>d</sub> is dominant. Small combinational logic: t<sub>skew</sub> is comparable with td.

18

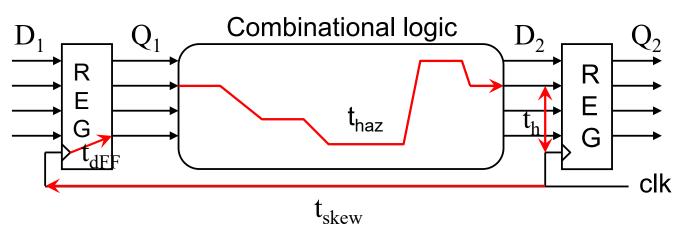

# Timing constraints of synchronous circuits 2

| t <sub>dFF</sub> : | Delay time of | of the register |

|--------------------|---------------|-----------------|

| ul l               | •             | 0               |

- $t_{haz}$ : Start time of hazards

- t<sub>skew</sub>: Clock skew

- t<sub>h</sub>: Hold tome of the register

$$t_h < t_{dFF} + t_{haz} + t_{skew}$$

(Hold time constraint)

When  $t_{skew} < 0$  (The arrival time of the clock signal to the output register is delayed), there is a risk of the malfunction.

#### 3.3.4 Clock generator

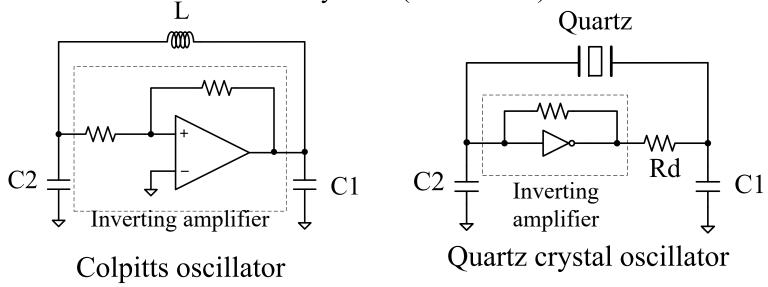

# Reference clock generator

- Principle of quarts crystal oscillator is the same as a Colpitts oscillator. The quarts resonator is electrically equivalent to the inductor in the Colpitts oscillator.

- A Q factor of quarts crystal resonators is normally over 100,000. Therefore, the effective digit of the oscillation frequency is 6 digits.

- Reference clock of digital systems

- Real time clock (32.768kHz)

- Reference clock of a wireless communication

- Reference clock of audio systems (5.6448MHz)

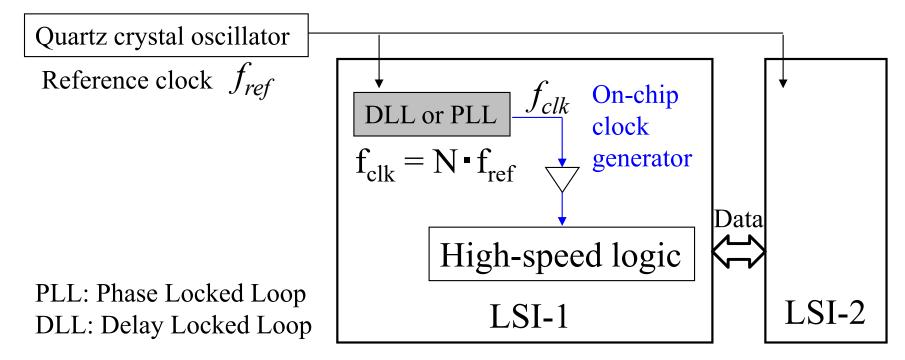

# Synchronization at the system level

- The internal clock in each LSI is synchronized to the reference clock (System clock).

- The reference clock frequency can be multiplied by PLL or DLL.

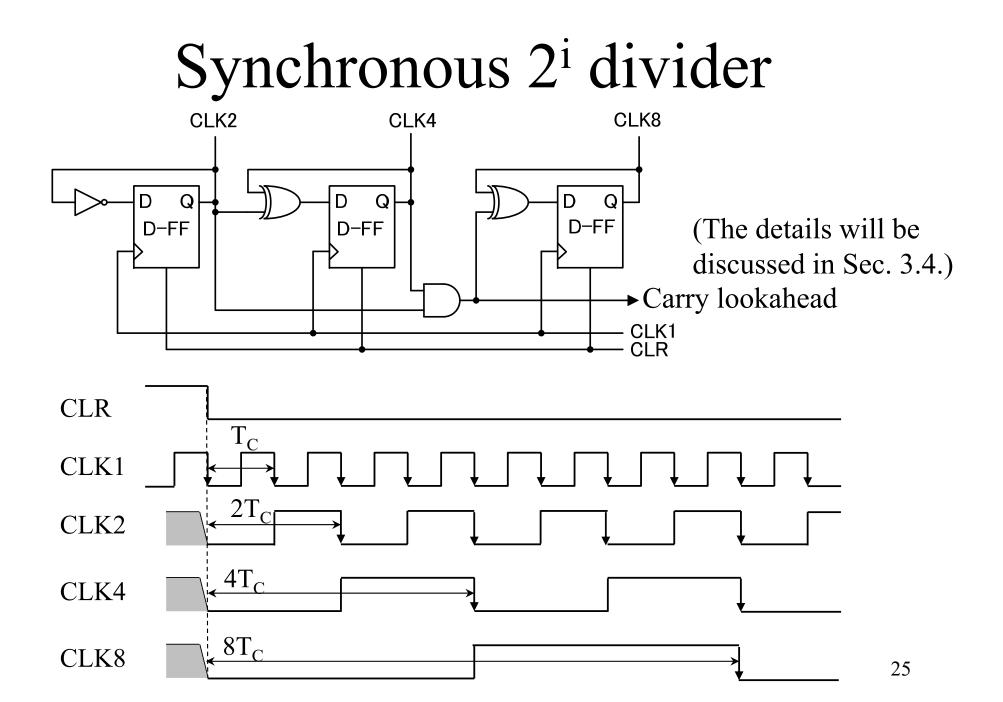

- The main clock signal in LSI is divided to the required frequency and distributed to the sub-systems.

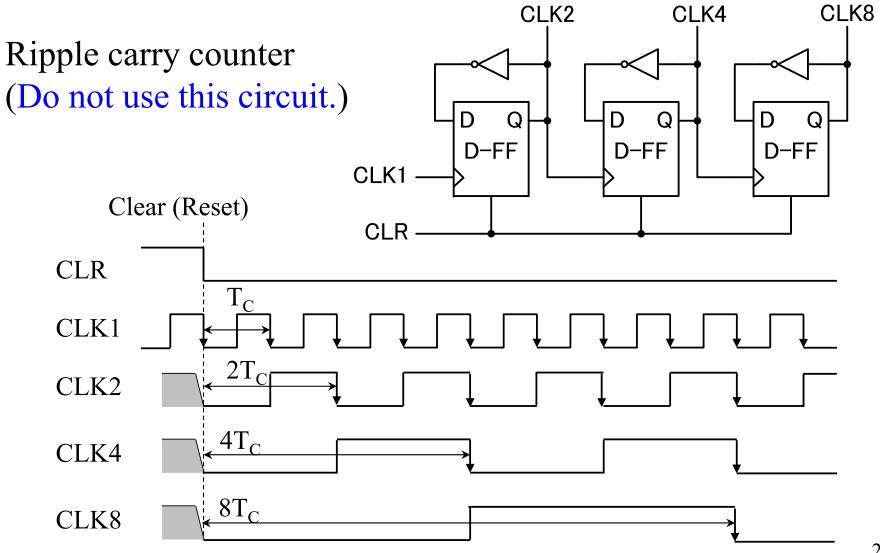

#### Asynchronous 2<sup>i</sup> divider