レイアウト設計には、回路図を作成したものと同じ統合開発環境を使用する。

vlsi> setlic Cadence IC6に相当する番号を入力 vlsi> setlic Mentor Calibreに相当する番号を入力 vlsi> cd ~/d vlsi> virtuoso &

- CIWのメニューから、Tools > Library Manager... を選択し、Library Managerを起動。

- Library Managerで、ライブラリLtickaをクリックして選択。

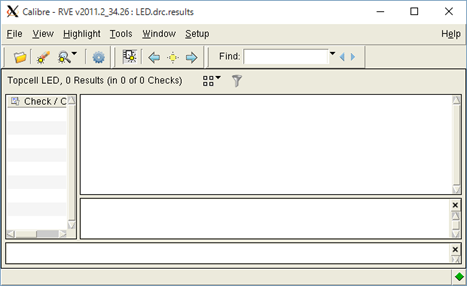

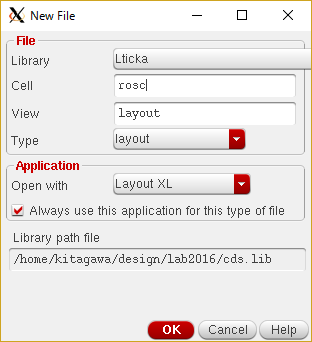

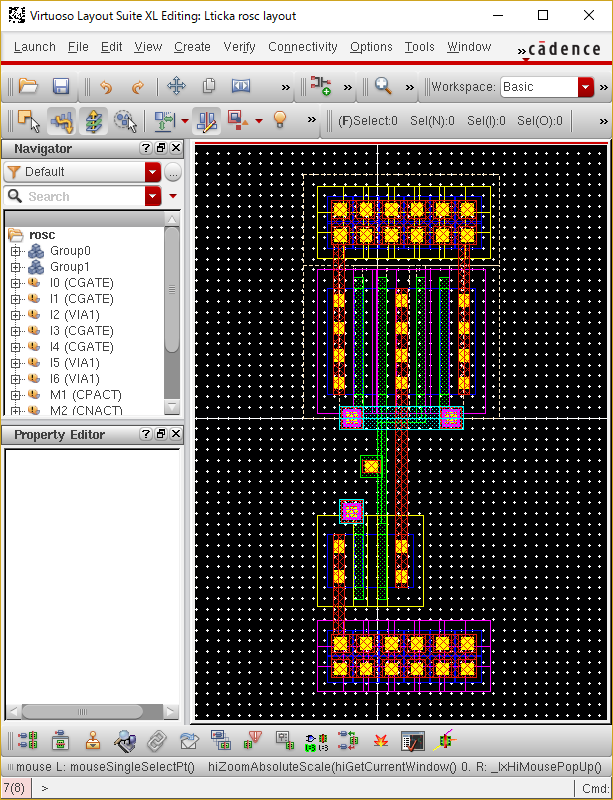

- Library Managerのメニューより、File > New > Cell View... を選択し、下図のように設定して、roscのlayout viewを作成。Typeは、layout、Open withは、Layout XL(レイアウトエディタ)とする。

- Library ManagerのView欄にlayoutが追加され、Virtuoso Layout Suite(レイアウトエディタ)が起動する

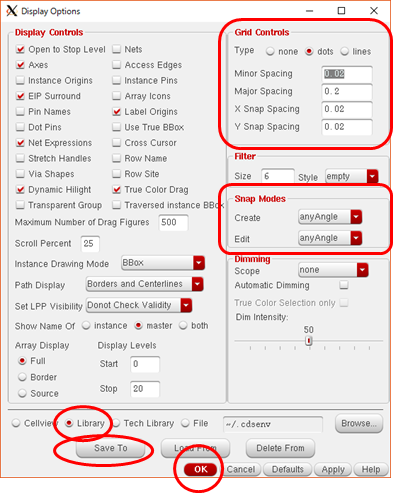

レイアウト設計がしやすいように、下記の設定をしておく。

- レイアウトエディタのメニューより、Options > Display... で、以下のグリッド設定を行う

- 許容されるグリッドの値は、使用テクノロジやレイヤーによって異なるが、ここでは、エラーが出ないよう余裕を持たせている。集積度を上げたいときは、設計規則を確認するとよい。

設定内容

Grid Controls - Minor Spacing 0.02 Grid Controls - Major Spacing 0.2 Grid Controls - X Snap Spacing 0.02 Grid Controls - Y Snap Spacing 0.02 Snap Modes - Create anyAngle Snap Modes - Edit anyAngle

以上の設定をライブラリLtickaに保存する。

- 下の方のLibraryのラジオボタンを選択。

- Save Toボタンをクリックしてから、OKボタンをクリック。

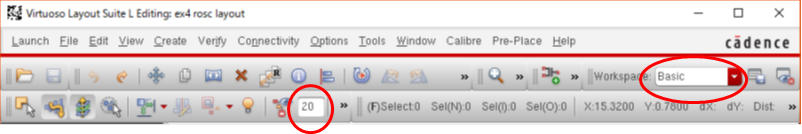

- レイアウトエディタのDisplay Stop Level(数字の書かれたツールボックス)を10に変更。

- Display Stop Levelは、表示する階層数を表す。値が小さいと、呼び出した部品の内容が表示されず外形表示となるが、描画が高速になる。通常は、10で十分。

- Work Space欄を、Basicに変更。

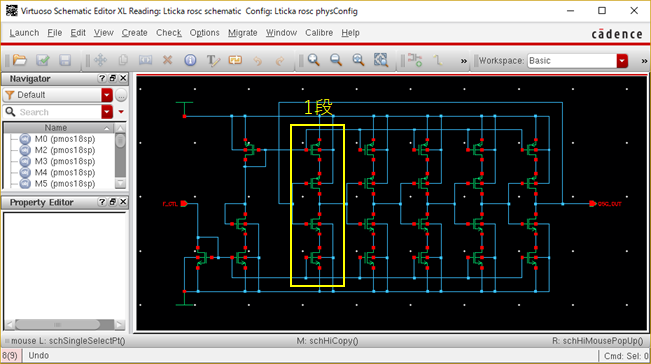

- レイアウトエディタと同時に回路図も開くので、これから設計する回路部分をドラッグして選択する。ここでは、リングオシレータ1段分の4個のMOSFETを選択する。

- 全体を選択してもよいが、多量にMOSFETのレイアウトが生成されるのでどれが、どれやら分からなくなるので、部分を絞った方がよい。

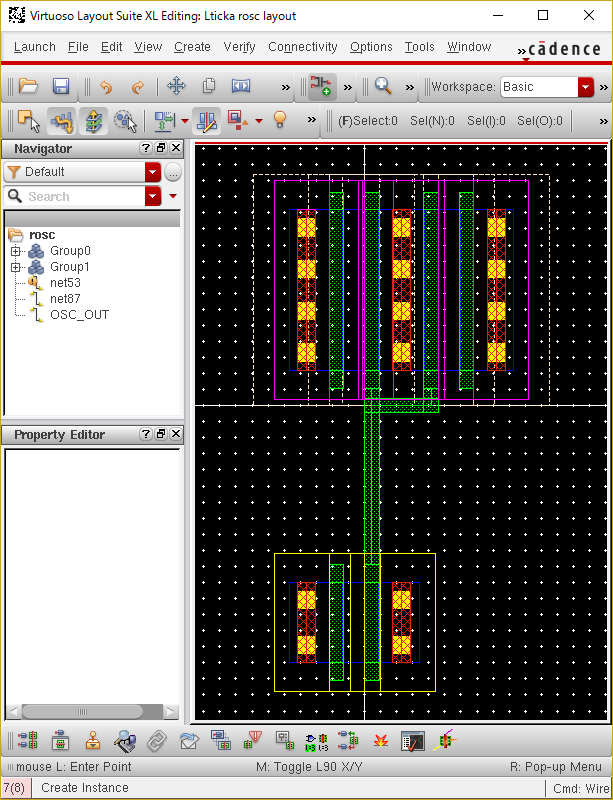

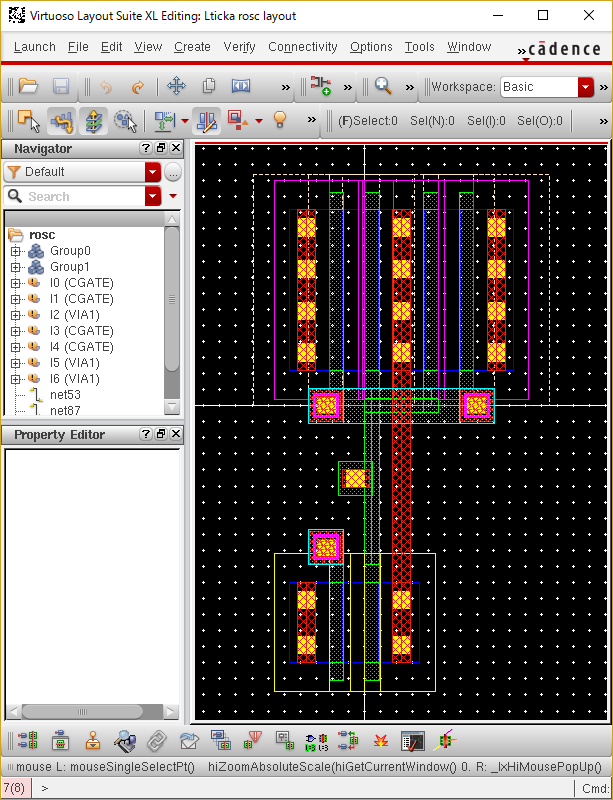

- レイアウトエディタの下側のツールボックスで、Generate Selected From Sourceアイコンをクリックすると、MOSFETのパターンが6個レイアウトウインドウに表示される。

- 回路図上のMOSFETは4個だが、p-ch MOSGEYはMultiplier = 2 なので、各MOSFETに2個のレイアウトが生成される(Multiplier = 並列接続数)。

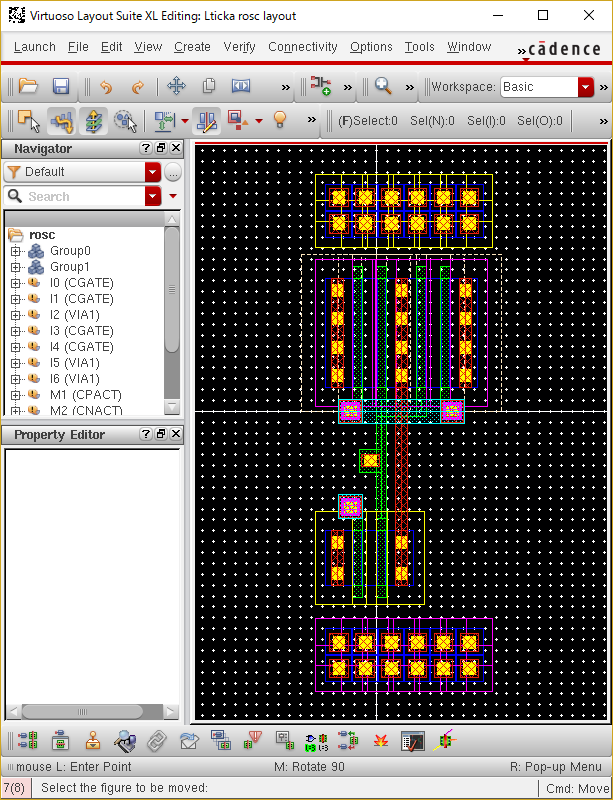

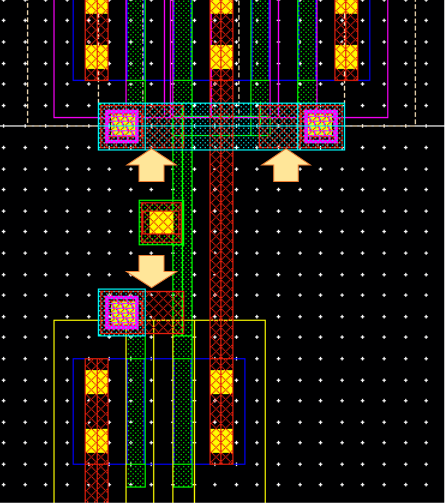

- 横に並んでいる2個のMOSFETを移動させ、ゲート電極を近づけアバットメントを行う。移動は、ツールバーのMoveボタンまたはmキーで実行できる。

- アバットメントは、並列または直列に接続された複数の同タイプMOSFETをマージさせる。詳しくは、集積回路工学第1の実習ページを参照。

- 直列接続されている2個のMOSFETの場合は2本のゲート電極が平行に並ぶ。

- 並列接続されている2個のMOSFETの場合は2本のゲート電極がコンタクト列を挟んで平行に並ぶ。

- 直列と並列の両方の接続がある場合は、直列のMOSFETを先にアバットメントした方がレイアウト面積は小さくなる。

- p-ch MOSFETは4個あるが、並列接続MOSFETが隣に初期配置されるので、直列接続のペアを探すこと。移動させようとすると、配線が表示されるの、どれが直列接続か判断できる。

- 直列接続のMOSGETをアバットメントしたら、2組のp-ch MOSFET をさらにアバットメントさせる。

- n-ch MOSFETの組とp-ch MOSFETの組をそれぞれ、ドラッグで選択して、グループ化しておく。グループ化は、ツールバーのCreate Groupボタンで実行できる。

- 配線のアイコン(Create Wire)をクリックしてから、接続を引き出したい場所をクリックすると、配線が引き出されるので、接続先までマウスカーソルを移動させてダブルクリックで終了。

- GATEの配線を実行。

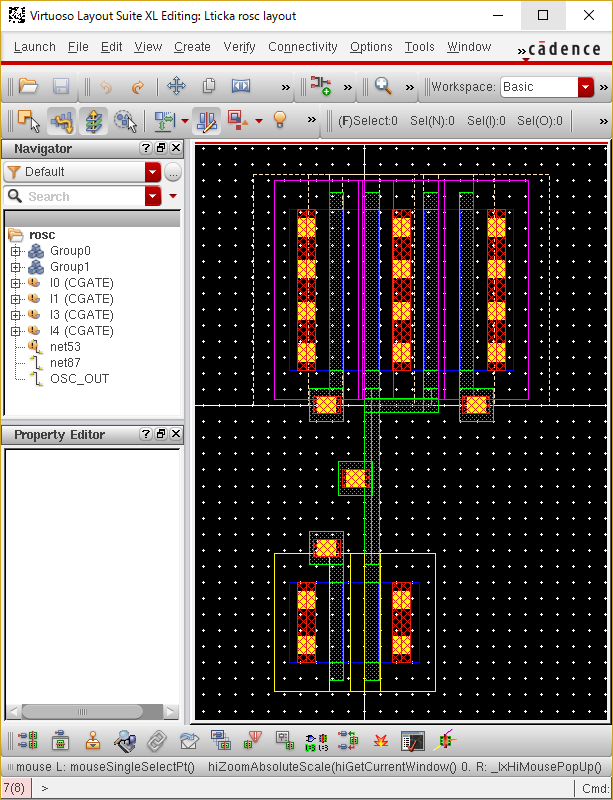

- GATE(ploy-Si)とMETAL1を接続するためのContactのパターンを配置。

- iキーを押して部品を呼び出す。ライブラリ= layoutLib, セル = CGATE

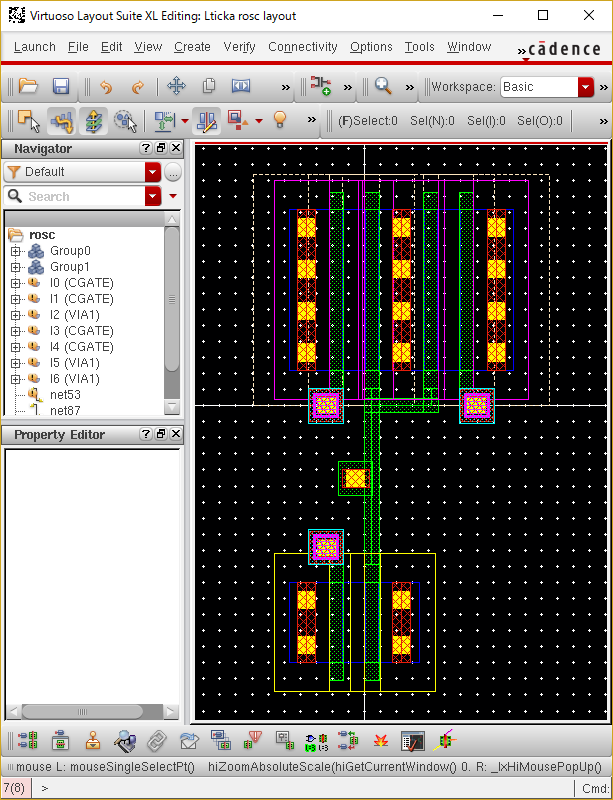

- METAL1とMETAL2を接続するためのVIA1のパターンを配置。

- iキーを押して部品を呼び出す。ライブラリ= layoutLib, セル= VIA1

- METAL1(赤)とMETAL2(シアン)の配線を行う。

- 複数の配線レイヤーがあるところをクリックすると、レイヤー選択ウインドウが表示されるので、配線を作りたいレイヤーの色を選択。

- 最小配線幅は、設計規則を確認すること。下記の図では、METAL2の幅を大きめにしてある。

- 配線幅の変更は、配線を引き出した後、右クリック > Options... で Create Wireフォームを表示させ、Width欄に値を入力。

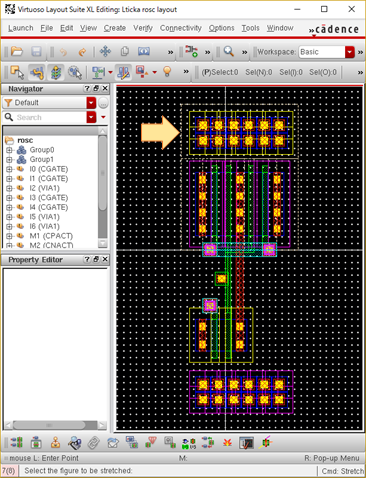

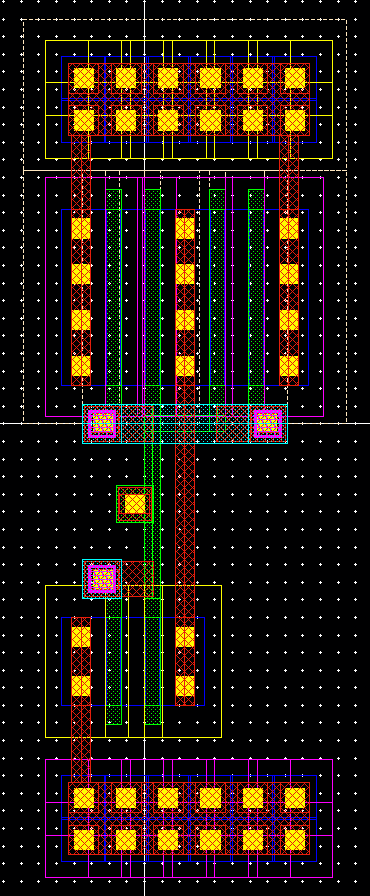

- NWELLへのコンタクトを作成。

- iキーを押して部品を呼び出す。ライブラリ= layoutLib, セル = CNACT

- Create Instanceフォームで、Rows = 2, Columns = 6, Delta Y = 0.48, Delta X = 0.48として、p-ch MOSFETの近くに配置(Delta X, Y の値について警告が出ることがあるが無視してよい)。

- P-Substrateへのコンタクトを作成。

- iキーを押して部品を呼び出す。ライブラリ= layoutLib, セル = CPACT

- Create Instanceフォームで、Rows = 2, Columns = 6, Delta Y = 0.48, Delta X = 0.48として、n-ch MOSFETの近くに配置。

[参考] 通常、NACTはp-substrate, PACTはNWELL内に配置し、NTAPはNWELL, PTAPはp-substrateに配置する。ただし、ACTIVEがNWELLの境界に近い場合、NACT, PACTと同じ設計規則が適用されるため、ここでは、NACTをNWELL内、PACTをp-substrateに配置した。

- 作成したCNACTの回りをNWELLで囲む。

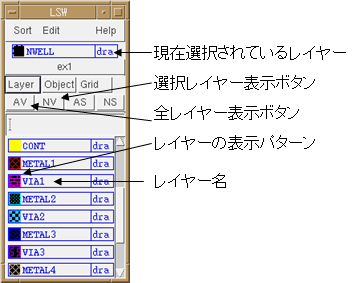

- LSW(レイヤーがリストされた縦長のウインドウ)で、NWELLを選択。

- Create > Shape > Rectangle(または、bキー)で配置。

- 適当な大きさの長方形を作成してから、ツールバーのStretchボタンまたはsキーで、辺をクリックして変形させると簡単に大きさの調整ができる。

- p-ch MOSFET用のNWELLとの間に隙間を空けないこと。

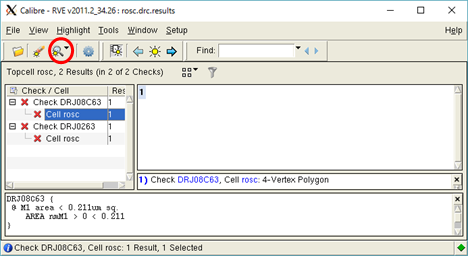

- ACTIVEとの距離が短か過ぎるとDRCエラーになるので注意。

LSW

- METAL1で、電源の配線を行う。

- LSWでMETAL1を選択。

- bキーで、CNACTとCPACTの上にMEATL1(赤)の長方形を描く。

- ツールバーのCreate Wireボタン(または CTRL + Shift + w)で、MOSFETのSource電極をCNACT,CPACT上の電源ラインに接続。

- METALの面積が小さすぎると、設計規則エラーとなるので、Rectangle(bキー)で、わざと伸ばしておく。

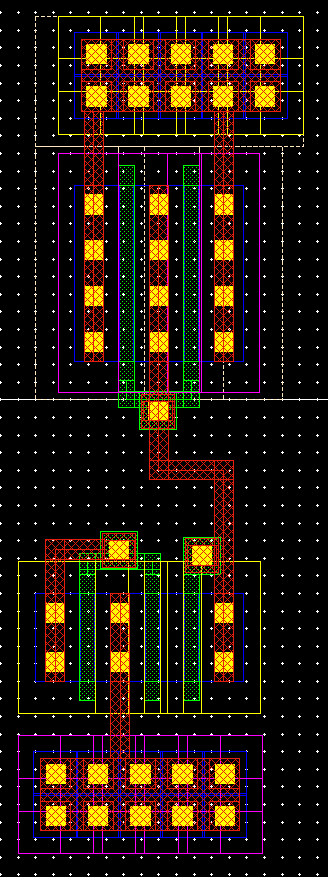

- 1段分の電流制御インバータが完成。

- レイアウトを保存。

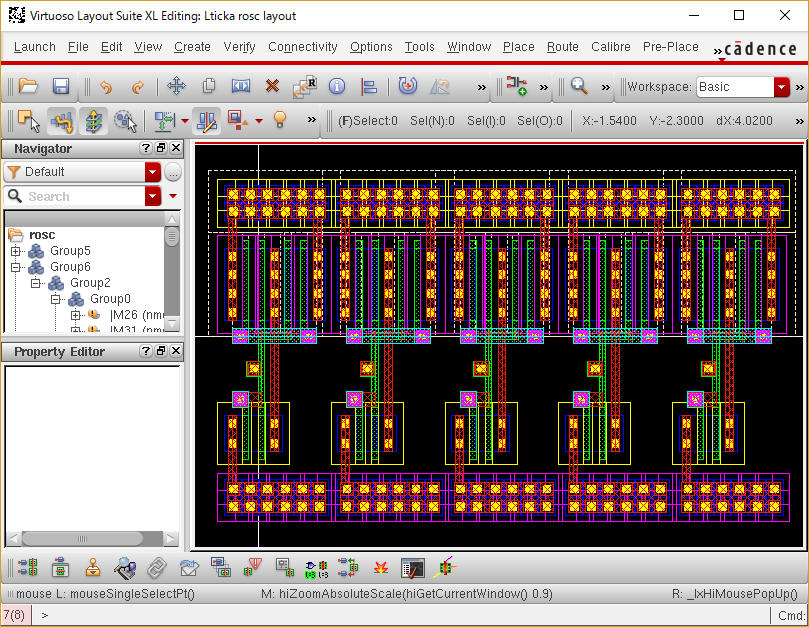

- 1段分の電流制御インバータを5個コピーして並べる。

- 1段分の電流制御インバータをドラッグして選択し、グループ化する。

- ツールバーのCopyボタンまたはcキーで、1段分の電流制御インバータをコピーして5個作る。

- 高さを揃えて配置する必要があるが、適当に配置して、後でそろえてもよい。そろえ方は、集積回路工学第1の実習ページを参照。

- 同じ要領で、カレントミラーのレイアウトを行う。

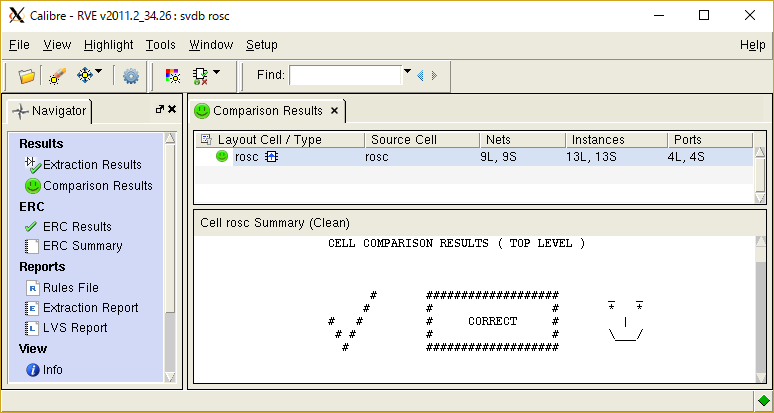

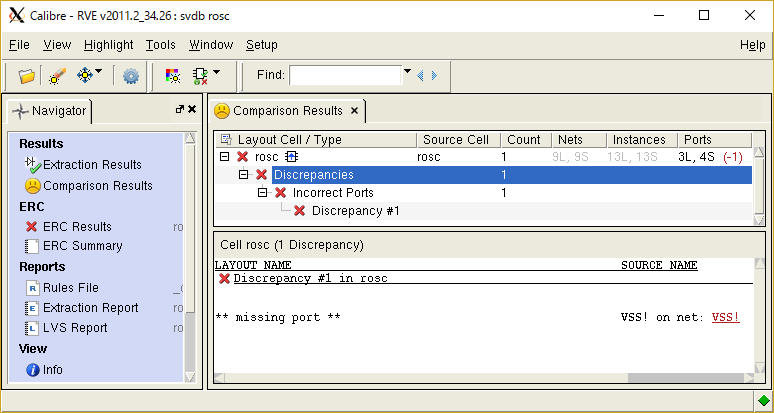

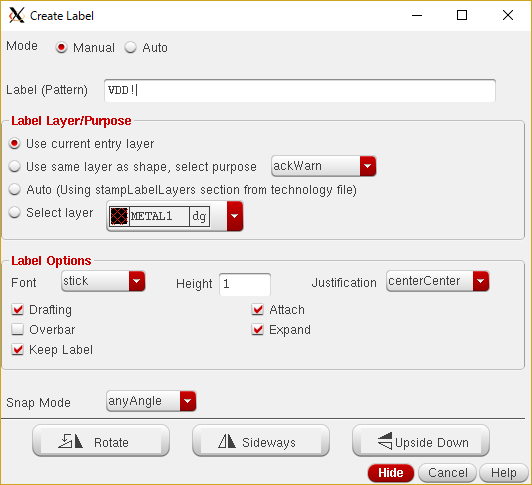

- ツールバーで、Create Labelボタンをクリックし、VDD!, VSS!, F_CTL, OSC_OUTのラベルを作成。配線層に合わせてラベル付けをする必要があるので、ここでは、ラベルを作成する前に、LSWで、METAL1を選択しておく。

- ラベルは、LVSのときに必要になる。

- ! は、グローバル配線であることを表す。! を付けないと、その階層だけのローカルな配線ラベルとして扱われる。

- リングVCO全体のレイアウト例

- レイアウトデータを保存